Техническая документация прояснила компоновку Ryzen 4000: два CCD, один ССX в CCD, 32 Мбайт L3 в CCX

Вчера вечером в Сети всплыл технический документ, описывающий некоторые характеристики ожидаемых процессоров Ryzen 4000, построенных на микроархитектуре Zen 3. В целом, никаких особых откровений он не принёс, но зато подтвердил многие предположения, которые высказывались ранее.

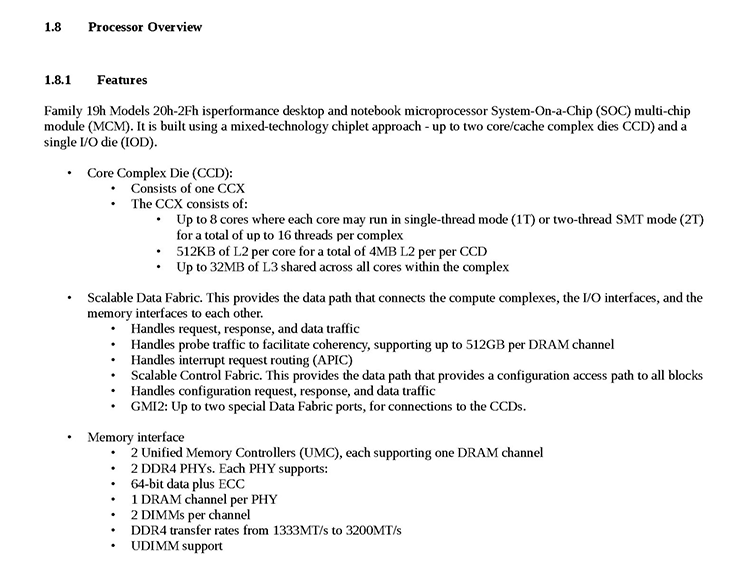

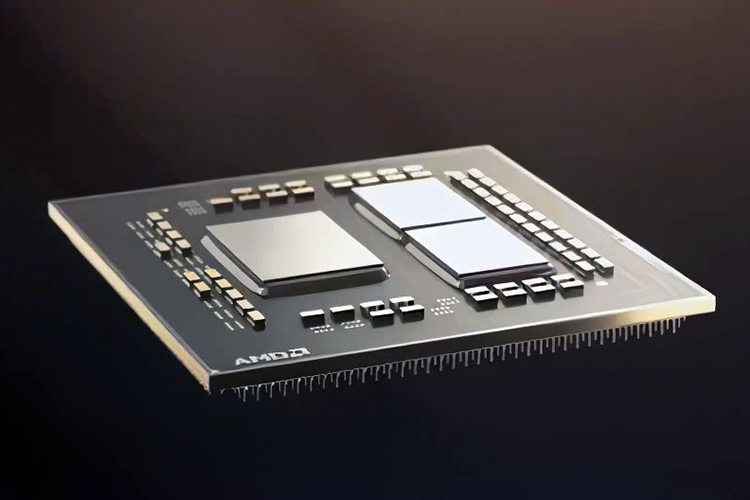

Согласно документации, процессоры Ryzen 4000 (кодовое имя Vermeer) сохранят чиплетную компоновку, введённую в их предшественниках поколения Zen 2. Будущие массовые процессоры, как это и было ранее, будут обладать чиплетом ввода-вывода и одним или двумя CCD (Сore Сomplex Die) — чиплетами, содержащими вычислительные ядра.

Ключевым отличием процессоров Zen 3 станет внутреннее строение CCD. В то время как сейчас в каждом CCD содержится по два четырёхъядерных комплекса CCX (Core Complex), каждый из которых располагает собственным сегментом L3-кеша объёмом 16 Мбайт, в Ryzen 4000 чиплеты будут состоять из одного восьмиядерного CCX. Объём L3-кеша в каждом CCX при этом будет увеличен с 16 до 32 Мбайт, однако к изменению общей ёмкости кеш-памяти это очевидно не приведёт. Восьмиядерные процессоры серии Ryzen 4000, которые теперь будут иметь в своём составе один CCD-чиплет, получат 32-Мбайт L3-кеш, а 16-ядерные CPU с двумя CCD-чиплетами будут располагать 64-Мбайт L3-кешем, составленным из двух сегментов.

Изменений в объёме L2-кеша ждать не нужно: на каждое из ядер процессора будет приходиться по 512 Кбайт кеш-памяти второго уровня.

Тем не менее, укрупнение CCX очевидным образом скажется на производительности. Каждое из ядер в Zen 3 получит прямой доступ к более ёмкой части кеш-памяти третьего уровня, а кроме того, большее число ядер сможет обмениваться данными напрямую, минуя Infinity Fabric. Это значит, что в Zen 3 снизятся задержки межъядерного взаимодействия, и уменьшится влияние на производительность ограниченной пропускной способности связывающей части процессора шины Infinity Fabric, а значит, в конечном итоге вырастет показатель IPC (число исполняемых за такт инструкций).

При этом ни о каком росте числа ядер в потребительских процессорах речь не идёт. Максимальное число ССD-чиплетов в Ryzen 4000 будет ограничено двумя, таким образом предельное число ядер в процессоре не сможет перешагнуть через 16.

Также не предвидится никаких принципиальных изменений с поддержкой памяти. Как следует из документа, максимальным официально поддерживаемым режимом для Ryzen 4000 так и останется DDR4-3200.

Никаких подробностей о составе модельного ряда и частотах входящих в него процессоров документация не сообщает. Более детальная информация очевидно станет известна 8 октября, когда AMD проведёт специальное мероприятие, посвящённое процессорам Ryzen 4000 и микроархитектуре Zen 3.